One of the main advantages of RISC-V architecture is that it is open, so any organization with the right skills can develop its own cores, and India’s government has taken up this opportunity with the Microprocessor Development Programme (MDP) helping develop VEGA RISC-V cores locally.

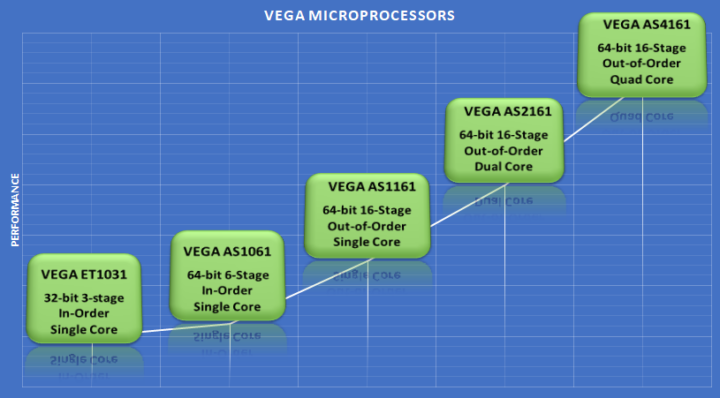

Thanks to funding by the Ministry of Electronics and Information Technology (MeitY), the Centre for Development of Advanced Computing (C-DAC) managed to design five RISC-V processors ranging from a single-core 32-bit RISC-V microcontroller-class processor to a Linux capable quad-core 64-bit out-of-order processor.

Key features of the five VEGA cores developed by the C-DAC:

- VEGA ET1031 – 32-bit single-core 3-stage in-order RV32IM processor with AHB/AXI4.bus, optional MMU, optional Debug

- VEGA AS1061 – 64-bit single-core 6-stage in-order RV64IMAFDC processor with 8KB D-cache, 8KB I-cache, FPU, AHB/AXI4 bus

- VEGA AS1161 – 64-bit single-core 16-stage pipeline out-of-order RV64IMAFDC processor with 32KB D-cache, 32KB I-cache, FPU, AHB/AXI4/ACE bus

- VEGA AS2161 – 64-bit dual-core 16-stage pipeline out-of-order RV64IMAFDC processor with 32KB D-cache, 32KB I-cache, 512KB L2 cache, FPU, AHB/AXI4/ACE bus

- VEGA AS4161 – 64-bit quad-core 16-stage pipeline out-of-order RV64IMAFDC processor with 32KB D-cache, 32KB I-cache, 1024KB L2 cache, FPU, AHB/AXI4/ACE bus

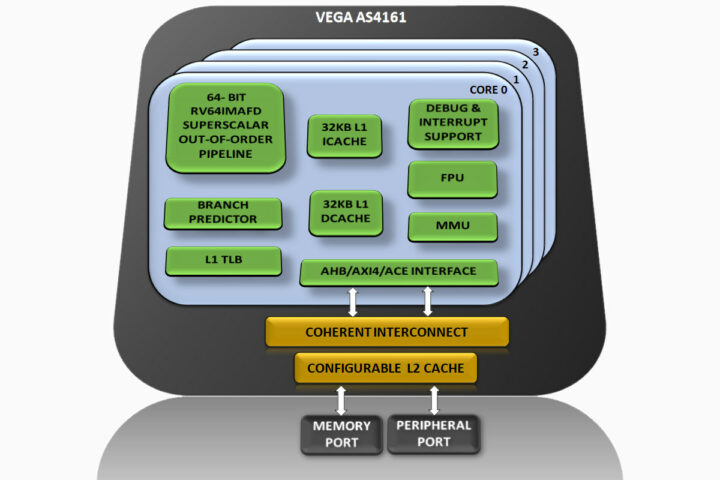

Looking more into the high-end VEGA AS4161 key features:

- RISC-V 64G (RV64IMAFD) Instruction Set Architecture

- 13-16 stage out-of-order pipeline implementation

- Advanced branch predictor: BTB, BHT, RAS

- Harvard architecture, separate Instruction, and Data memories

- User-, Supervisor- and Machine-mode privilege levels

- Fully-featured memory subsystem with Linux support

- Memory Management Unit

- Page-based virtual memory

- Configurable L1 cache

- Configurable L2 cache

- High-performance Multi core Interconnect

- High-performance IEEE 754-2008 compliant floating-point unit

- AXI4- / ACE, compliant external interface

- Platform level Interrupt Controller

- up to 127 IRQs

- Low interrupt latency

- Vectored interrupt support

- Advanced Integrated Debug Controller

- JTAG compliant interface

- HW/SW breakpoints support

- Debug extension allowing Eclipse debugging via a GDB >> openOCD >> JTAG connection

- Linux compatible

We should not expect a processor for desktop Linux anytime soon, as AS4161 mostly targets storage and networking applications.

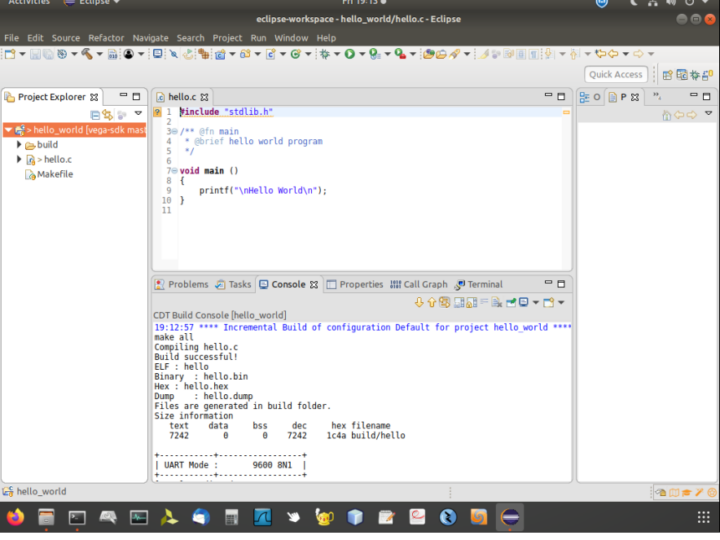

What’s even better is the public availability of the documentation for two SoCs – THEJAS32 and THEJAS64 – based on respectively VEGA ET1031 and VEGA AS1061 cores, with the HDL code running on ARTY A7 FPGA board (A7-35T can run THEJAS32, but A7-100T is needed for THEJAS64). The C/C++ VEGA SDK with an Eclipse IDE allows engineers to develop programs for the platform, and Linux source code for the 64-bit VEGA processors is also provided. The code is hosted on Gitlab, but you need to request access before retrieving the code… That’s a bit disappointing.

The Indian government also plans to host training sessions for the VEGA processors, but that page is currently empty. I was unable to find any information about the schedule for VEGA silicon and whether manufacturing would take plan in India. The project’s blog hasn’t been updated for several months, but the “VEGA Processor”‘s YouTube account uploaded a video on January 31, 2022, giving an overview of the five VEGA RISC-V processors.

More details can be found on the project’s website.

Via Reddit.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress