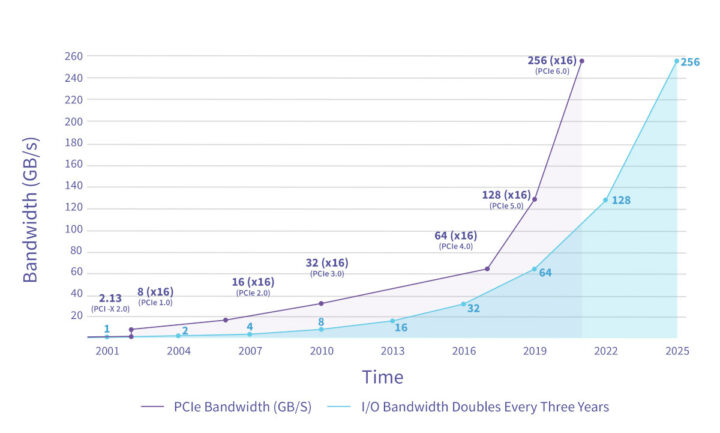

The PCI-SIG has just released the PCIe 6.0 specification reaching 64 GT/s transfer speeds, or 256GB/s, doubling the PCIe 5.0 specification data rate, and aimed at Big Data applications in the data center, artificial intelligence/machine learning, HPC, automotive, IoT, and military/aerospace sectors.

PCIe 6.0 follows PCIe 5.0 announced in 2019 and can achieve the 256GB/s data rate in a 16-lane configuration. Implementation will take time, as even PCIe 5.0 is not widely used yet, and in the embedded space, I only found PCIe 5.0 in the recently announced Alder Lake-S Desktop IoT processors, with the Alder Lake Mobile IoT processors still being limited to PCIe 4.0.

- 64 GT/s raw data rate and up to 256 GB/s via x16 configuration

- Pulse Amplitude Modulation with 4 levels (PAM4) signaling, leveraging existing PAM4 already available in the industry

- Lightweight Forward Error Correct (FEC) and Cyclic Redundancy Check (CRC) mitigate the bit error rate increase associated with PAM4 signaling

- Flit (flow control unit) based encoding supports PAM4 modulation and works in conjunction with the FEC and CRC to enable double the bandwidth gain

- Updated Packet layout used in Flit Mode to provide additional functionality and simplify processing

- Low latency and reduced bandwidth overhead.

- Maintains backward compatibility with all previous generations of PCIe technology

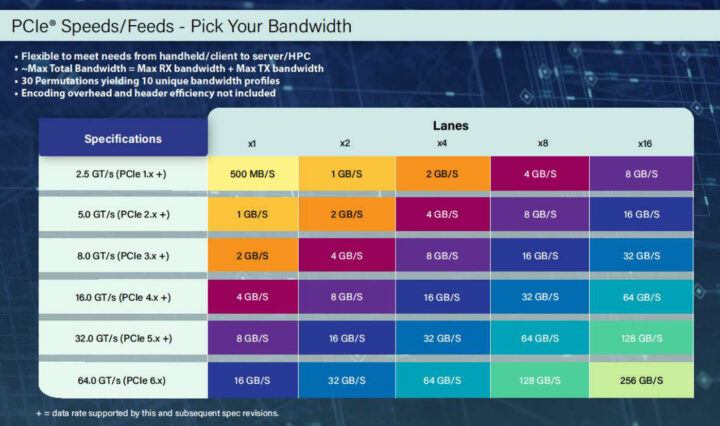

I’m glad I found the handy table above, as I’m always confused with the speed delivered by specific versions of PCIe and the number of lanes. I don’t expect to write much about PCIe 6.0 any time soon though. Most Arm processors we cover here only started to come with a PCIe 2.1 interface a few years ago starting with Allwinner H6 in 2017, and the PCIe implementation did not work that well. The Rockchip RK3588 octa-core processor that should become available this year features a much faster 4-lane PCIe 3.0 interface that should deliver up to 8GB/s. PCIe 3.0 was introduced in 2010, so if it takes as much time for the new PCIe specification to be implemented into mid-range processors, I can’t wait to write about the latest Rockchip RK3988 processor with PCIe 6.0 once it comes out in 2032!

You’ll find more details about PCIe 6.0 on the PCI-SIG website.

Via Liliputing and Anandtech

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress