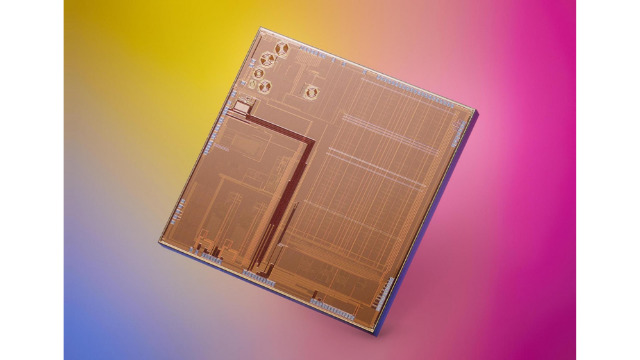

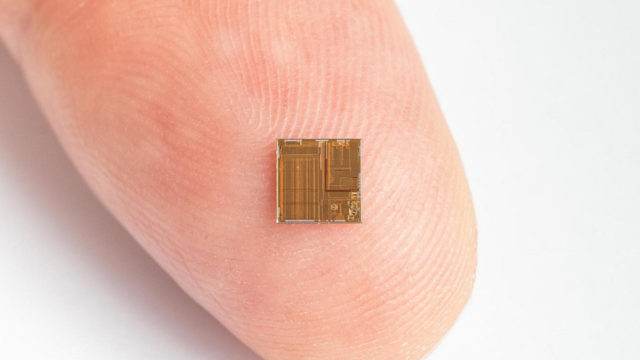

CSEM and USJC together have developed an ultra-low-power RISC-V chip for electronic gadgets such as wearables. The semiconductor companies, from Switzerland and Japan respectively, have been in the market for a while, developing technologies for low-power chips. Their latest collaboration uses Adaptive Body Biasing (ABB) and Deeply Depleted Channel (DDC) to build an ultra-low-power RISC-V chip with all the required and necessary components.

Originating from the labs of CSEM, the Adaptive Body Biasing dwells into the operating efficiency of all the modes of ON, Standby, and OFF. There has been the problem of power leakage in Standby and OFF operating modes, but the Adaptive Body Biasing technology helps design to minimize power leakage when the processor is not operating while keeping the best performance in ON mode.

For most of the designs, the processor is in Standby mode waiting for the incoming data or the next event to be offered. At such times there is a significant amount of power leakage that might reduce the performance of the chip. Adaptive Body Biasing used to design this ultra-low-power chip reduces the amount of power leakage in these periods. With the limited resources available at the moment, EENews Europe have claimed the power consumption to be as low as 10µA in slow mode (see below), and in standby mode, the consumption is about 1pW/bit.

The system-on-chip operates at a threshold voltage of 0.6V and is built with 55nm C55DDC process technology. The ultra-low-power chip features the icyflex-V RISC-V core with an integrated 256KB RAM and 4KB ROM. A technical report published in 2019 by the CSEM scientist tells us more about the ultra-low-power processor based on RISC-V Architecture. This 4-stage pipeline architecture implements the RV32IMC ISA that supports compressed instructions and multiplications.

Coming back to the newly developed RISC-V chip support mode switching in real-time that helps to maintain power efficiency along with performance. The system-on-chip has the capability of coexisting various versions of low-power (for slow and retention modes) and high-speed (for fast mode). More details provided by EENews Europe tell us that the SoC is by default in slow mode at 50 kHz and can be switched to fast mode at 8 MHz. The most awaited parameter, the power consumption by the SoC is 10 µA for the slow mode and 250 µA for the fast mode. In the time of inactivity, the chip is observed to consume about 1µA at the always-on 32KHz clock.

If you are interested in the press release, please visit the CSEM press room page.

Abhishek Jadhav is an engineering student, RISC-V Ambassador, freelance tech writer, and leader of the Open Hardware Developer Community.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress