SiFive Performance P550 was supposed to be the most powerful RISC-V core to date, capable of outperforming Arm’s Cortex-A75 core in raw performance, but especially in terms of efficiency, with three times the performance per mm2.

But there may be an even more powerful RISC-V processor, albeit developed as a research project, with the Chinese Academy of Science (CAS)’s XiangShan open-source processor presented at the recent RISC-V World Conference China 2021 with the goal of matching Cortex-A76 performance.

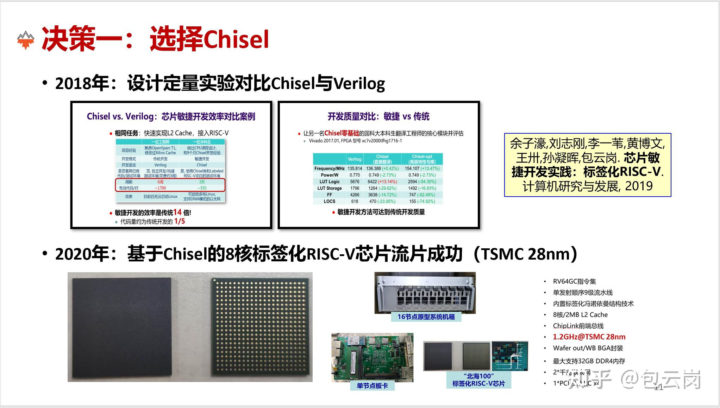

The project was launched on June 11, 2020, and 25 classmates and teachers participated in the development of Xiangshan with 821 main branch code mergers, 3296 code submissions, more than 50,000 lines of code, and more than 400 documents, mostly in Chinese only for now.

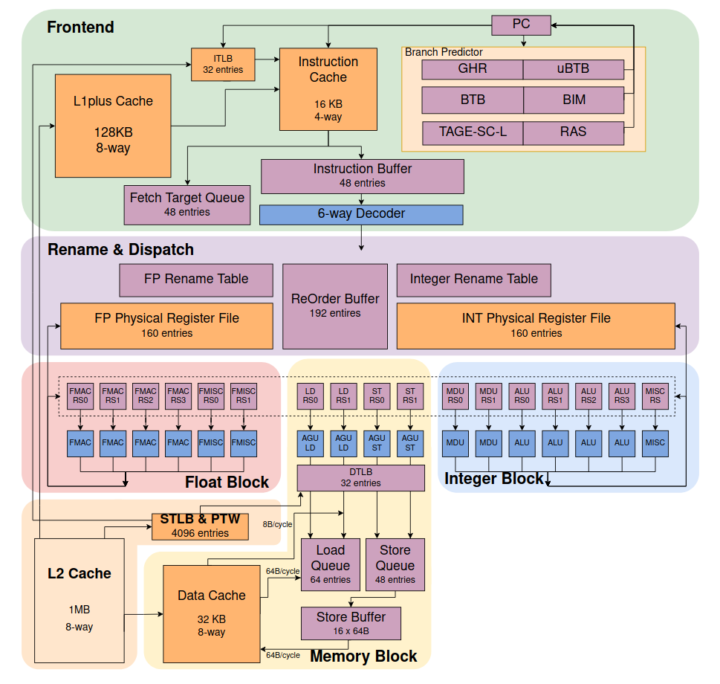

This culminated with an 8-core prototype built based on Yanqihu () architecture using TSMC’s 28nm process with the processor running up to 1.2 or 1.3 GHz that should be taped out this month. But plans have been made to tape out a new prototype based on Nanhu () by the end of the year, using SMIC’s 14nm process allowing up to 2 GHz frequency, and further iterations of the architecture will aim at rivaling Arm’s Cortex-A76 processor.

The current implementation relies on RV64GC RISC-V architecture, includes 2MB cache, PCIe interface, and supports up to 32GB DDR4 memory. The XiangShan processor has been tested with Debian on an FPGA platform, and eventually, it may end up supporting Ubuntu which recently ported to HiFive RISC-V boards.

The RISC-V core has been developed with the Chisel language, which the developers claim requires five times fewer lines of code than Verilog, and much faster to develop with, according to a recent post in Zhihu (in Chinese). You can find the source code released under a Mulan PSL v2 license (Mulan Permissive Software License, Version 2), and some documentation in English and Chinese on Github.

Since it’s a university project, it’s unclear whether it will ever be used commercially, but considering the Chinese government is looking for alternatives to x86 and Arm, I would not be surprised if XiangShan ends up in a processor for the Chinese market.

Via Heise

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress