There’s a lot of interest/hype around RISC-V, and low-cost boards such as Longan Nano or Maixduino are already available, but those are based on microcontroller-class chips, even though it’s possible to run Linux on Kendryte K210 RISC-V board, it comes without MMU, so it’s not for everyone.

Linux capable RISC-V boards do exist but cost several hundred dollars or more with the likes of HiFive Unleashed and PolarFire SoC Icicle development kit. If only there was a RISC-V board similar to the Raspberry Pi board and with a similar price point… The good news is that the RISC-V International Open Source (RIOS) Laboratory is collaborating with Imagination technologies to bring PicoRio RISC-V SBC to market at a price point similar to Raspberry Pi.

The PicoRio board was presented at the RISC-V Global Forum on September 3rd. I could not find the full presentation slides yet, but there are some screenshots here and there on Twitter giving us a few more details.

PicoRIo preliminary specifications:

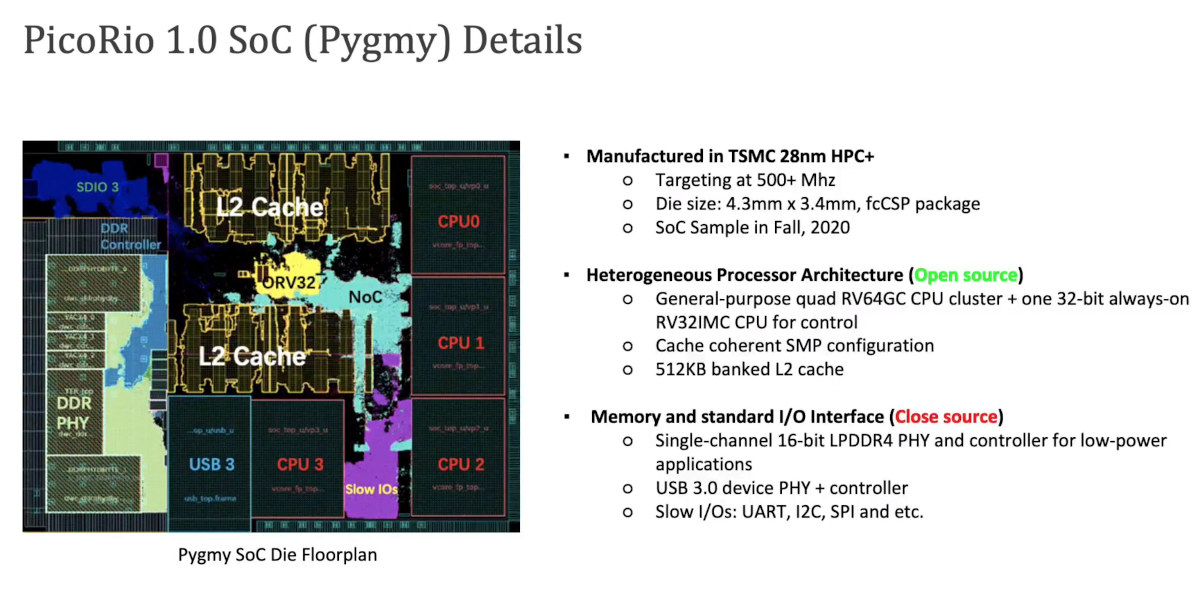

- PicoRio SoC

- Quad-core 64-bit RISC-V (RV64GC) processor at 500+ MHz

- 1x 32-bit RISC-V (RV32IMC) always-on core

- Imagination Technologies PicoRio GPU (only in second revision of chip)

- 512KB L2 cache

- Package – 4.3 x 3.4 mm die size , fcCSP package

- 28 nm Process

- System memory – 16-bit LPDDR4

- Storage – TBD, likely MicroSD card

- Video Output – TBD

- USB – USB 3.0 interfaces

- I/Os – UART, I2C, SPI, etc…

PicoRio aims to be open-source hardware as much as possible, with the CPU part being fully open, but the memory PHY, USB 3.0 PHY, GPU, and other I/Os will still be closed source, even though the goal is to eventually have as much IP released under a BSD-like open source license.

The board will target the Raspberry Pi price, but be more efficient with battery-powered devices in mind. PicoRio will run Linux, and support higher-level languages like WebAssembly and JavaScript.

More details should eventually surface on RIOSLab website that is currently very much work-in-progress…

Thanks to Arnaud for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress