In Arm’s world, heterogeneous processors are pretty common, with for example big.LITTLE / dynamIQ application processors mixing powerful Cortex-A7x cores with power-efficient Cortex-A5x cores., or “industrial” processor such NXP i.MX 8M family with Cortex-A53 application cores combined with Cortex-M4F real-time core.

Maybe I did not follow enough, but I hadn’t really seen anything equivalent in MIPS world, except if we count Ingenic T31 with RISC-V and MIPS cores. That is until today where I was informed about documents related to Ingenic X2000 IoT application processor with two 32-bit MIPS Xburst 2 core, one MIPS Xburst 0 real-time cores, as well as up to 256MB RAM built-into the SoC.

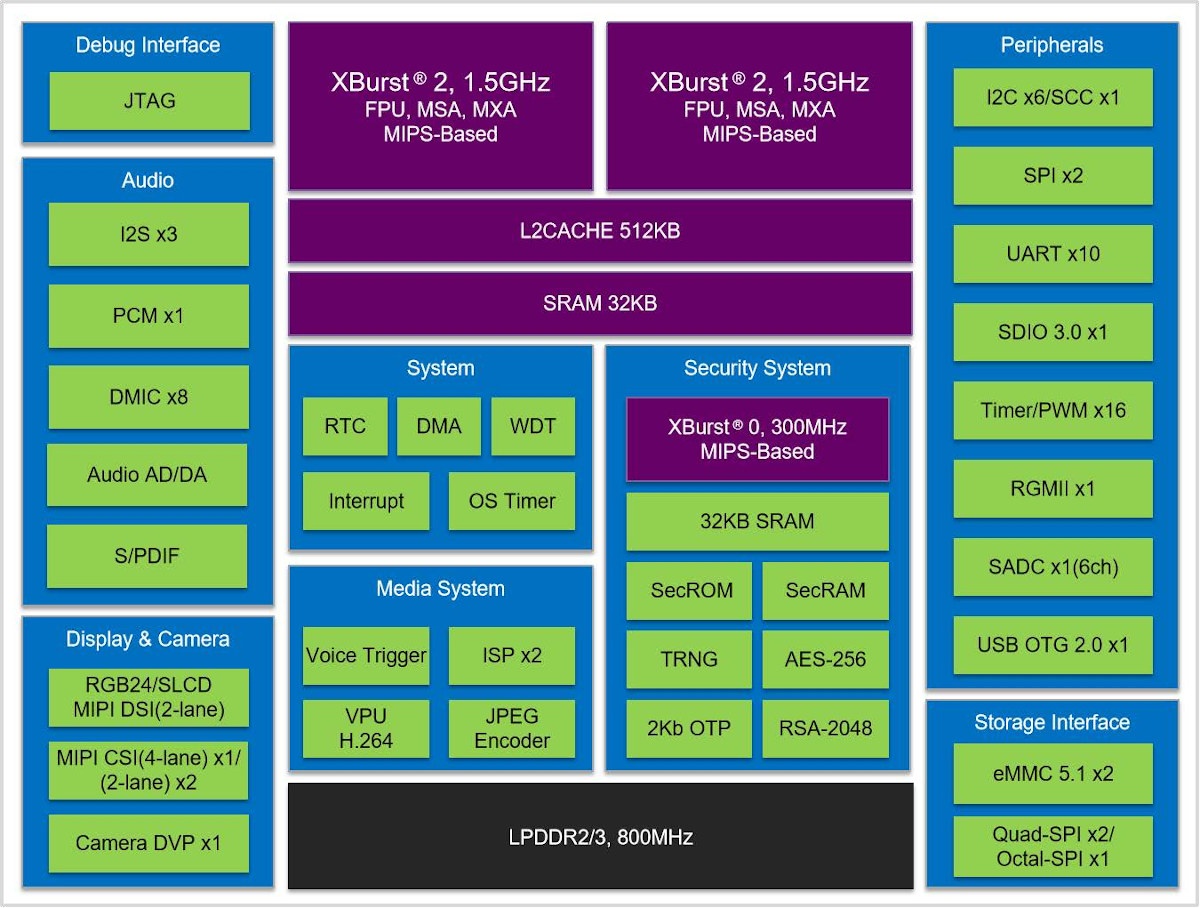

Ingenic X2000 specifications:

- CPU Core – Dual XBurst 2, MIPS ISA based, frequency up to 1.5 GHz with 32KB L1 x2 Cache, 512KB L2 Cache, 32KB SRAM, FPU,128bit SIMD

- MCU Core – XBurst 0 MIPS core @ 300MHz for security and real-time control

- System Memory -128/256MB LPDDR2/3 in package

- Storage I/F

- SPI Flash Controller supporting Quad & Octal SPI

- 2x MMC/SD/SDIO

- Display Interfaces

- MIPI-DSI up to 1920×1080 @ 40Hz

- SLCD up to 640×480 @ 60Hz, 24BPP

- RGB up to 1280×720 @ 60Hz, 24BPP

- Video Processing Unit (VPU)

- H.264 encoder/decoder up 1920x1080p30

- JPEG encoder/decoder up to 70Mega-pixels/s

- Camera Subsystem

- Image Signal Processor

- 8-bit/10-bit/12-bit YUV422 DVP interface up to 1280×720 @ 30 fps

- 4-lane or 2x 2-lane MIPI CSI interface up to 1080p120

- Supports synchronization of dual-camera sensor

- Audio Processor

- Digital Microphone Array Controller supporting 8 mic channels with

voice triggering - 3x I2S, PCM interface, S/PDIF

- Digital Microphone Array Controller supporting 8 mic channels with

- Networking – Gigabit Media Access Controller, in compliance with IEEE 1588-2002

- USB – 1x USB 2.0 OTG

- Security – True Random Number Generator and AES-256/RSA-2048/MD5/SHA/SHA2 part of MCU core sub-system

- Other Peripherals

- 16x PWM

- Interrupt controller supporting 64 sources

- Watchdog, Real-time clock

- 6-channel 10-bit A/D converter

- GPIO

- 6x I2C, 2x Synchronous serial interfaces (SSI)

- 10x UART

- Power Consumption – 300mW typ.

- Package – BGA270 – 12 x 12 x 1.2mm, 0.65mm Pitch

- Process – 28nm

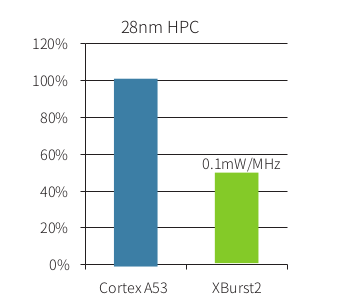

Ingenic X2000 also happens to be the very first processor with XBurst 2 cores, a core that was announced many years ago as a MIPS64 (64-bit MIPS core), but finally, the company decided to completely change the design with MIPS32 ISA R5. Ingenic claims Xbust2 is twice as power-efficient as Arm Cortex-A53 core with the same 28nm process.

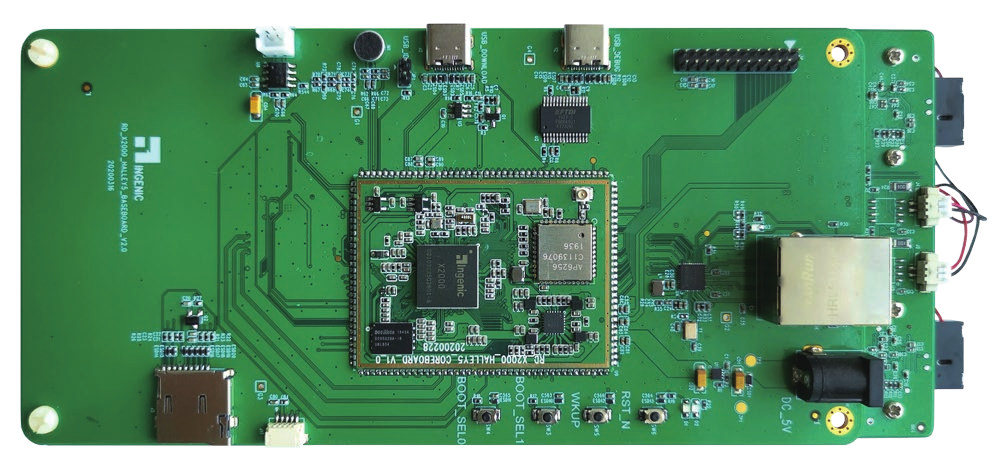

The company can provide a complete software and hardware development kit with a Linux 4.4 BSP and Halley5 development board with an X2000 SoM with a wireless module fitted to a largish carrier board with Ethernet, USB, microphone, MicroSD card slot, I/O header, buttons and so on. The other side of the board is equipped with a dual-camera board and a Full HD AMOLED display.

Last April, we asked whether MIPS was dead, at least outside of China with Linux kernel maintainers leaving, a lawsuit, and bankruptcy. We however still noted some MIPS related changes in Linux 5.7 last month, but with a very minimal changelog. So that should mean you’d have to rely on Ingenic BSP, and IMHO mainline support is very unlikely.

There’s no product page on Ingenic website, but we have something even better in their FTP server with the SoC and board product briefs and a datasheet in English and /or Chinese.

Thanks to Alex for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress