A while ago, I was informed three new Marvell processors had made it to mainline Linux, namely CN9130, CN9131, and CN9132, but at the time, the description was a bit cryptic:

The CN9130 is made of one AP807 and one internal CP115. There are three development boards that are made of this SoC:

* CN9130-DB

* CN9131-DB (with one additional modular CP115 compared to CN9130-DB)

* CN9132-DB (with two additional modular CP115 compared to CN9130-DB)

No other public information was available either, but Marvell has now published more details and those are OCTEON TX2 Infrastructure processors with four Cortex-A72 cores @ 2.2 GHz, up to 18x SERDES IO, and 10GbE.

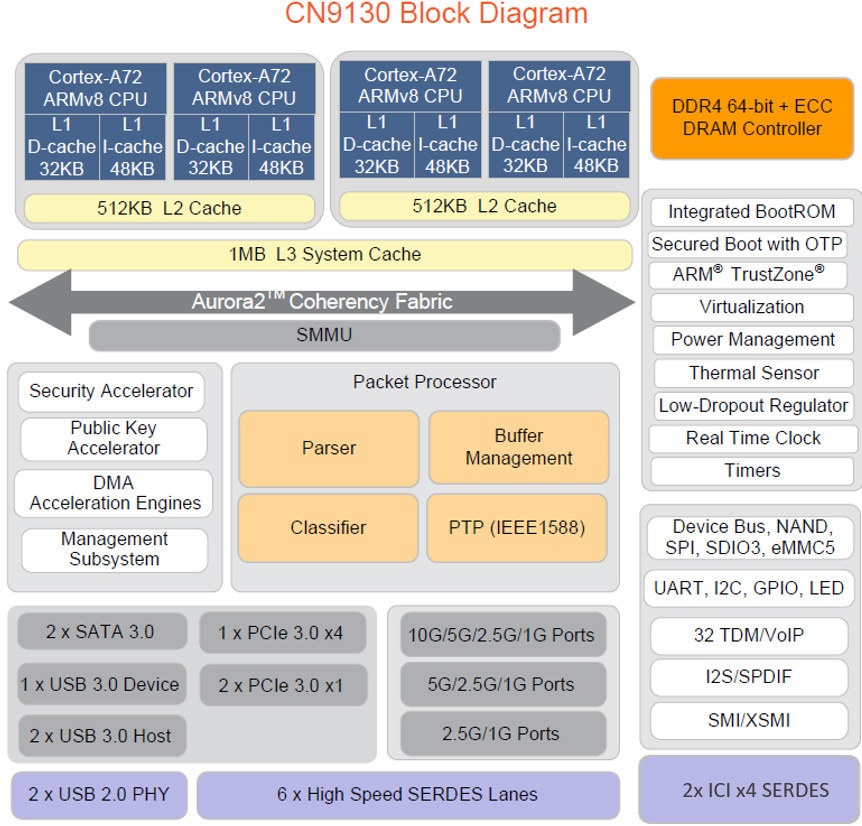

Octeon TX2 CN9130 key features and specifications:

- CPU – Quad-core Armv8 Cortex-A72 @ up to 2200 MHz with 48 KB I-cache, 32 KB D-cache, 1 MB total L2 cache divided into two clusters of 512 KB ECC shared cache, 1MB L3 Cache with ECC

- Memory I/F – 64-bits DDR4 + ECC at 1200Mhz clock

- PCIe 3.0 – 1x Port x4 + 2x Ports x 1; total of 3 controllers and up to 6 lanes

- Ethernet Ports – 1x 10/5 GbE port + 2x 1/2.5 GbE Ports or 2x 5 GbE Port +

1x 1/2.5 GbE Port - USB 3.0 – 2 x USB 3.0 (Host/Device)

- SATA 3.0 – 2 x SATA 3.0

- SERDES Lanes – 6 Lanes

- Network Subsystem

- Configurable packet processor

- I/O Virtualization Flexible parsing and classification

- IPv4 and IPv6 N-Tuple classification

- QoS, Buffer Management

- Energy-efficient Ethernet

- Virtualization

- Armv8-A virtualization

- IO virtualization, sing SMMUv2 with stage 1 and stage 2 translations

- Virtualized DMA engines

- Virtualized Security engine

- Virtualized packet processor

- PCIe with SR-IOV support

- Package – HFCBGA 24×24 mm, 0.8 mm pitch

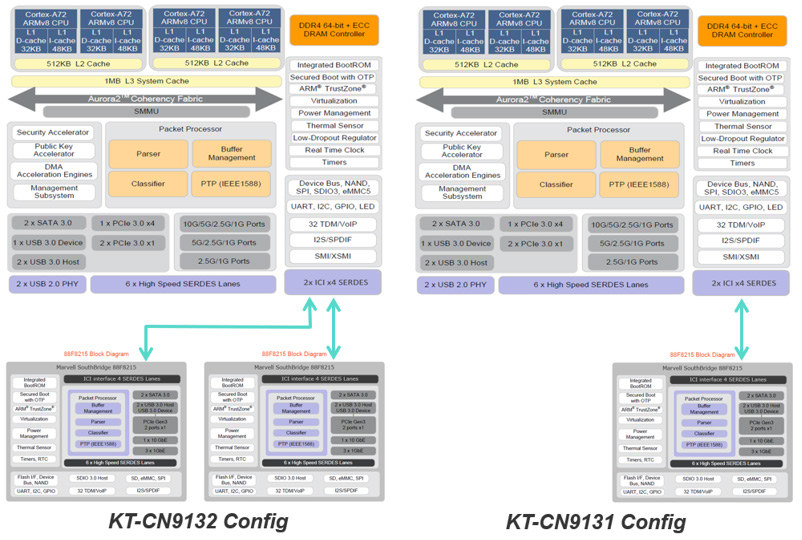

CN9131 and CN9132 add respectively one and two 88F8215 bridge chips that doubles and triples I/O’s (PCIe, Ethernet, USB, SATA and SERDES) compared to CN9130 processor. The CN913x dies are all integrated into a single multi-chip module (MCM) package comprised of an application processor (AP) and one or more Southbridge (SB).

The processor are expected to be found in 5G base stations, network and security appliances such as firewalls or routers & gateways, as well as IoT/edge servers, enterprise/SDN switches, and various networked storage solutions.

More details can be found on the product page, as well as a recent press release also covering Octeon Fusion CNF95xx SoCs built around Octeon TX2 processors and designed for “4G and 5G layer 1 baseband processing”, as opposed to “Layer 2 and 3 transport and control plane processing” for the processors covered in this article.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress