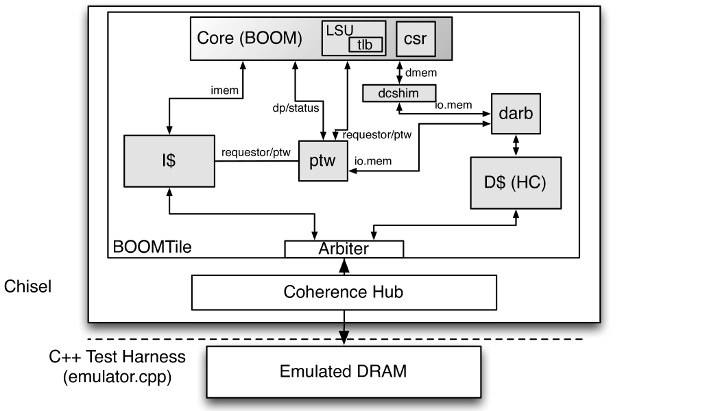

The Berkeley Out-of-Order Machine (BOOM) is an open source RV64G RISC-V core written in the Chisel hardware construction language, and mainly ASIC optimized. However, it is also usable on FPGAs, and developers support the FireSim flow to run BOOM at over 90 MHz on Xilinx Ultrascale+ FPGAs found in Amazon EC2 F1 instances.

The BOOM core was created at the University of California, Berkeley in the Berkeley Architecture Research group, in order to create a high performance, synthesizable, and parameterizable core for architecture research.

- ISA – RISC-V (RV64G)

- Synthesizable

- FPGA support

- Parameterized

- Floating Point (IEEE 754-2008)

- Atomic Memory Op Support

- Caches & Virtual Memory

- Boots Linux

- Privileged Arch v1.11

- External Debug

BOOM is said to be inspired by the MIPS R10k and the Alpha 21264 out–of–order processors, based on a unified physical register file design (aka as “explicit register renaming”). The source code for the core can be found on Github, and documentation here, which also details how to get started.

More details may also be found on boom-core.org website.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress