SiFive has recently announced their Core IP 7 Series of RISC-V cores offering better performance, and designed to enable “embedded intelligence” in applications such as 5G, networking, storage, augmented reality, artificial intelligence, SLAM, and sensor fusion.

Three families of the new 7 Series been launched with namely SiFive E7, S7 and U7 Core IP Series, so let’s have a look at each of them.

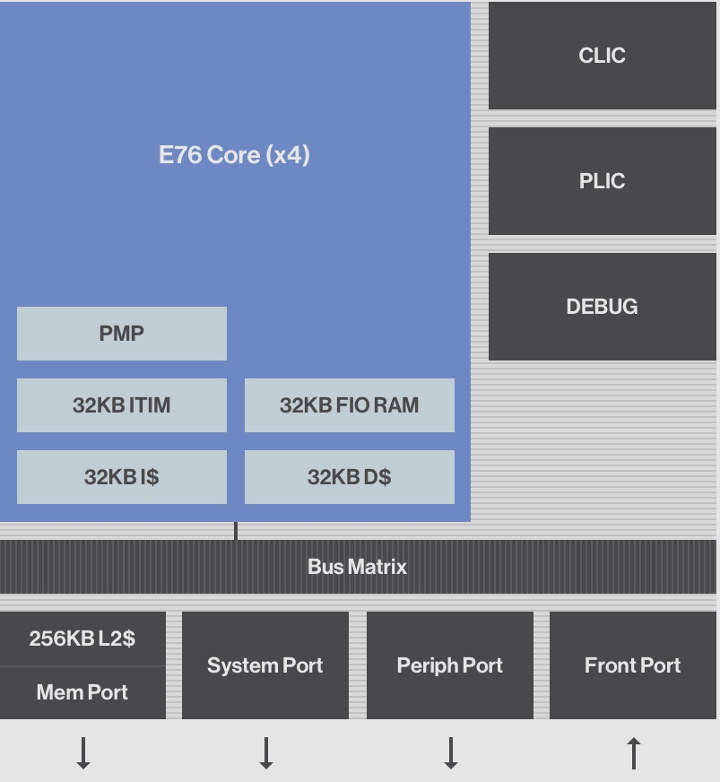

E7 Core IP Series – E76 and E76-MC Cores

The E7 Core IP Series comprises the 32-bit E76 and E76-MC (Multi-core), provides hard real-time capabilities, and compares to Arm’s Cortex M7, Cortex-R7/R8 cores.

E76-MC Key Features

- Fully compliant with the RISC-V ISA specification

- 4x RV32IMAFC E76 Cores

- Machine and User Mode Support

- In-order, 8-stage pipeline

- Advanced Memory Subsystem

- 32KB Instruction Cache

- 32KB Instruction Tightly Integrated Memory (ITIM)

- 32KB Data Cache

- 32KB FIO RAM

- 256KB L2 Cache

- High-performance TileLink Interface

- Benchmark Scores- 2.3 DMIPS/MHz, 4.9 CoreMark/MHz

E76 is basically the same but with one core, no L2 cache, and no PLIC (Platform Level Interrupt Controller).

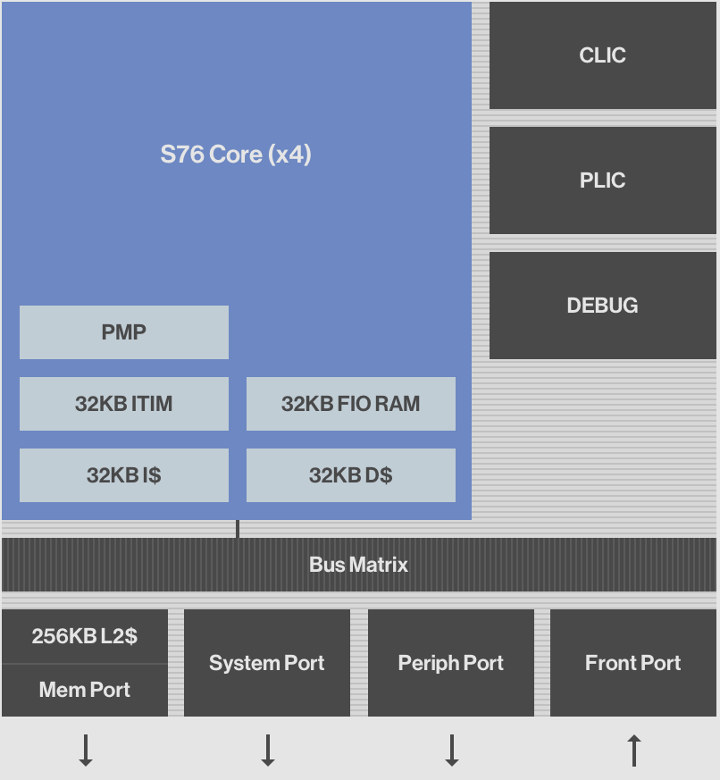

S7 Core IP Series – S76 and S76-MC Cores

The SiFive Core IP S7 Series also compares to Arm’s Cortex M7 and Cortex R7/R8 cores, but S76 and S76-MC cores are based on a high performance 64-bit architecture instead.

- Fully compliant with the RISC-V ISA specification

- 4x RV64GC S76 Cores

- Machine and User Mode Support

- In-order, 8-stage pipeline

- Advanced Memory Subsystem

- 32KB Instruction Cache

- 32KB Instruction Tightly Integrated Memory (ITIM)

- 32KB Data Cache

- 32KB FIO RAM

- 256KB L2 cache

- Efficient and flexible interrupts

- Physical Memory Protection (PMP)

- High-performance TileLink Interface

- Benchmarks – 2.5 DMIPS/MHz, 4.9 CoreMark/MHz

Again the S76 core is the single core version without L2 cache, nor PLIC.

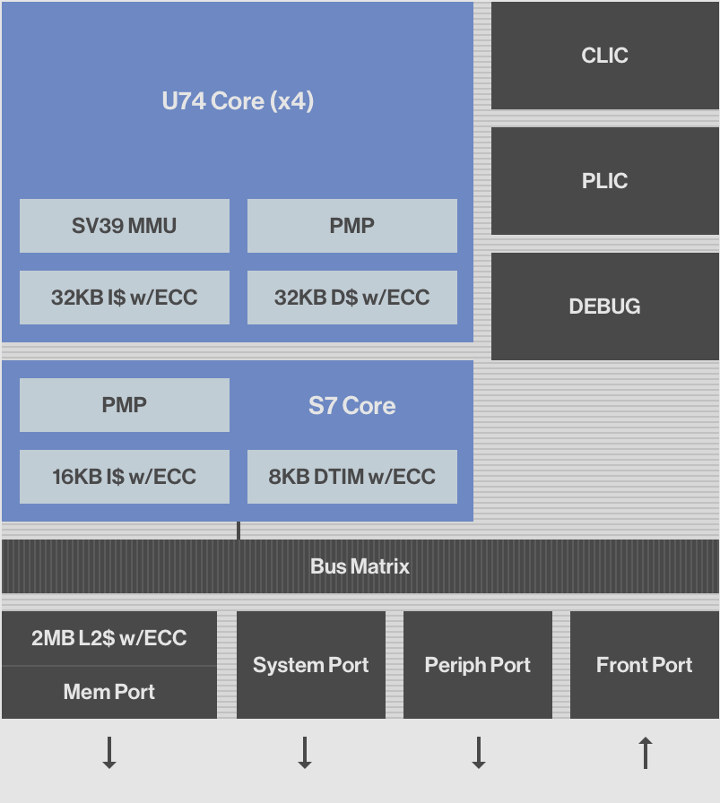

U7 Core IP Series – U74 and U74-MC Cores

Like other SiFive U-series RISC-V processor such as Freedom U540, the SiFive Core IP U7 Series is a Linux-capable applications processor. As such the 64-bit U74 and U74-MC processor cores support Linux, and compare to Arm’s Cortex A55 processor.

U74-MC Key Features:

- Fully-compliant with the RISC-V ISA specification

- 4x RV64GC U74 Application Cores with 32KB L1 I-cache with ECC, 32KB L1 D-cache with ECC, 8x Region Physical Memory Protection, Sv39 Virtual Memory support with 38 Physical Address bits

- 1x RV64IMAC S7 Monitor Core with 16KB L1 I-Cache with ECC, 8KB DTIM with ECC, 8x Region Physical Memory Protection

- U74 and S7 cores are fully-coherent

- Integrated 2MB L2 Cache with ECC

- CLIC for timer and software interrupts

- PLIC with support for up to 128 interrupts with 7 priority levels

- Real-time Capabilities – The L1 Instruction Cache and the L2 Cache can be configured into high-speed deterministic SRAMs

- Debug with instruction trace

- Benchmark Scores – 2.5 DMIPS/MHz, 4.9 CoreMark/MHz

The single core version – U74 – does not include a monitor core, and comes with 128KB L2 cache, instead of 2MB for U74-MC.

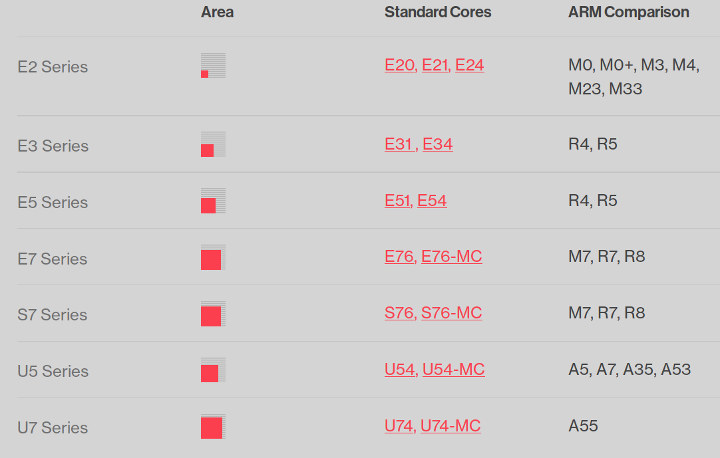

You’ll find further details on SiFive’s Core Designer page. It may be a little confusing to remember all new SiFive parts, so the company has provided a comparison table which you can refer to.

So that means SiFive now offers RISC-V cores competing with most of recent Arm cores, except for the most powerful Cortex-A7x cores like Cortex-A76, but I suppose that’s the next stage.

So that means SiFive now offers RISC-V cores competing with most of recent Arm cores, except for the most powerful Cortex-A7x cores like Cortex-A76, but I suppose that’s the next stage.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress