Goldmont Plus is the microarchitecture found in Gemini Lake processors, and products are just starting to get to market as we’ve seen with our recent Intel June Canyon NUC mini PC review.

But we already know the successor of the microarchitecture thanks to a programming document entitled “Intel Architecture Instruction Set Extensions and Future Features Programming Reference” which references “Future Tremont and later” micro-architecture.

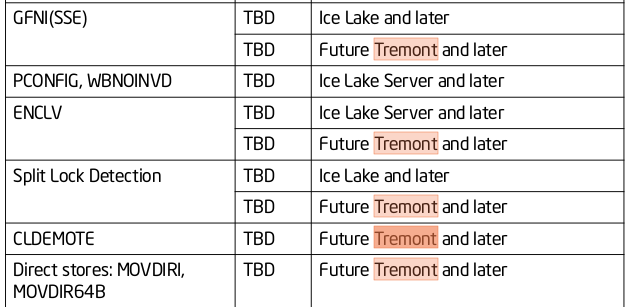

Here the full list of new instructions listed in the document:

- CLWB – Force cache line write-back without flush

- GFNI – Galois Field New Instructions

- ENCLV – SGX oversubscription instructions

- Split Lock Detection – detection and cause an exception for split locks

- CLDEMOTE – Cache line demote instruction

- Direct store – MOVDIRI and MOVDIR64B

- User wait – TPAUSE, UMONITOR, UMWAIT

That does not give much clue, but Wikichip found a patch submitted to the Linux Kernel mailing list on March 1st, that reveals a bit more:

Add perf core PMU support for Intel Tremont CPU cores:

– The init code is based on Goldmont plus.

– There is a new cache event list, based on the Goldmont plus cache event list.

– PDIR on fixed counter 0

– new topdown events

– OFFCORE_RESPONSE mask updates – Adaptive PEBS? (no code change)

So Tremont definitely looks like the successor of Goldmont Plus micro-architecture, and if we look some part of the code:

|

1 2 3 4 5 6 7 8 9 |

diff --git a/arch/x86/include/asm/intel-family.h b/arch/x86/include/asm/intel-family.h index b4d37ffa..aa4c026 100644 --- a/arch/x86/include/asm/intel-family.h +++ b/arch/x86/include/asm/intel-family.h @@ -63,6 +63,7 @@ #define INTEL_FAM6_ATOM_GOLDMONT 0x5C #define INTEL_FAM6_ATOM_DENVERTON 0x5F /* Goldmont Microserver */ #define INTEL_FAM6_ATOM_GEMINI_LAKE 0x7A +#define INTEL_FAM6_ATOM_JACOBSVILLE 0x86 |

JacobsVille should be an an “Atom class” processor, and the successor of either Gemini Lake or Denverton (server) processors. Some parts of the patch also refer to “10 nm”, so it could mean JacobsVille processors will be manufactured using a 10nm process, an upgrade from the 14nm process used for Gemini Lake processors.

That’s all I found for now, and products based on JacobsVille processors should probably not be expected before 2019.

Thanks “Anonymous” for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress