We first covered SiFive when they unveiled their open source Freedom RISC-V SoCs. Since then, they moved away from open source for their customizable IP, since their customers did not require fully open source designs, but kept releasing more RISC-V cores such as 32-bit E31 Coreplex & 64-bit E51 Coreplex, as well as offering their one-time fee pricing without recurring royalties, contrary to what some competitors – such as Arm – are doing.

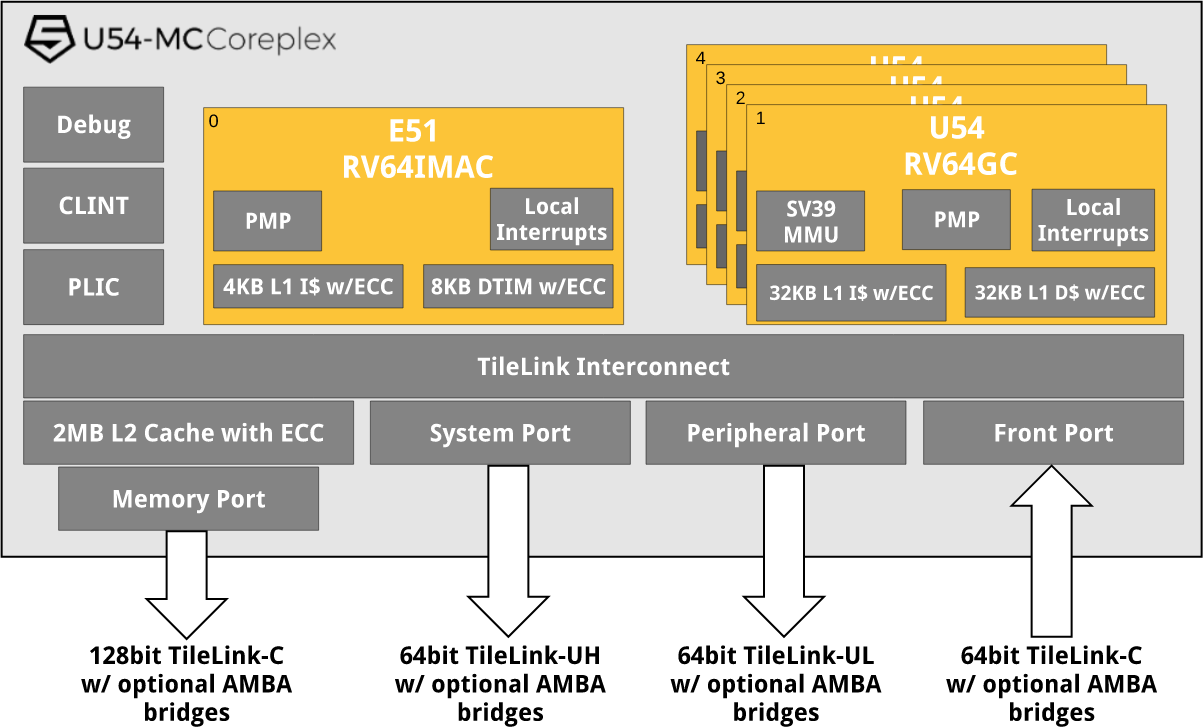

The company has now just announced U54-MC Coreplex quad core real-time capable application processor with support for full featured operating systems such as Linux.

U54-MC Coreplex main specifications / features:

- Fully compliant with the RISC-V ISA specification

- 4x RV64GC U54 Application Cores

- 32KB L1 I-cache with ECC, 32KB L1 D-cache with ECC

- 8x Region Physical Memory Protection

- 48x Local Interrupts per core

- Sv39 Virtual Memory support with 38 Physical Address bits

- 1x RV64IMAC E51 Monitor Core

- 4KB L1 I-Cache with ECC

- 8KB DTIM with ECC

- 8x Region Physical Memory Protection

- 48x Local Interrupts

- Fully Coherent TileLink Bus

- Integrated 2MB L2 Cache with ECC

- Real-time capabilities – Both the L1 Instruction Cache and the L2 Cache can be configured into high speed deterministic SRAMs

- CLINT for multi-core timer and software interrupts

- PLIC with support for up to 511 interrupts with 7 priority levels

- Debug with instruction trace

- U54 Performance – 1.7 DMIPS/MHz; 2.75 CoreMark/MHz

U54-MC Coreplex has been taped out as part of Freedom Unleashed platform with all 5 cores, including U54 and E51, running at over 1.50 GHz and manufactured using 28nm technology. The company compares it to Arm Cortex A35 cores in the table below which shows the added features.

| U54-MC Coreplex | ARM Cortex-A35 |

|---|---|

| RV64GC M + S + U Mode |

ARMv8-A, AArch32, AArch64 |

| 16 bit instructions | AArch32 only |

| Physical Memory Protection (PMP) and MMU | None, MMU only |

| Real-time capable | Not applicable |

| E51 Monitor Core | Requires additional IP |

| Integrated interrupt controller | Requires additional IP |

More details about the U54-MC Coreplex can be found on the product page, and the company plans to release an U54-MC Coreplex development board in Q1 2018.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress