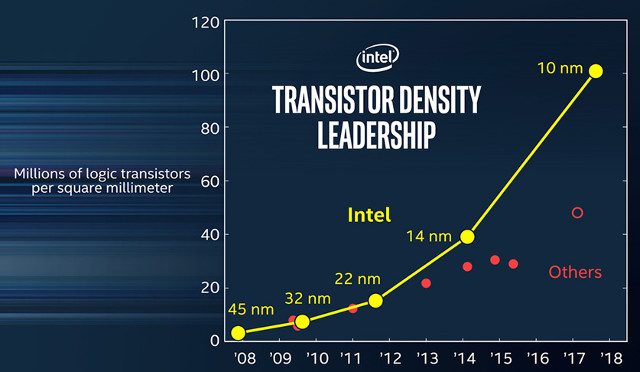

Process technology is important as the lower the process node, the more efficient the processor becomes, which leads to either longer battery life for the same tasks on battery powered devices, or allows for higher frequencies extracting more performance. Qualcomm and Samsung recently announced Snapdragon 835 SoC was manufactured using 10nm process technology, but Mark Bohr, an Intel Senior Fellow and director of process architecture and integration at Intel Corporation. wrote a blog post explaining that while in the past process node size and density were progressing in a “linear” fashion, this is not the case anymore, as marketing has changed, and some companies advance node names, even in cases where there’s minimal or no density increase.

The chart above implies that some companies 10nm process is barely better than Intel’s 14 nm process, with their 10nm process capable of integrating about twice as much transistors per square millimeter compare to competitors’ 10nm process.

The chart above implies that some companies 10nm process is barely better than Intel’s 14 nm process, with their 10nm process capable of integrating about twice as much transistors per square millimeter compare to competitors’ 10nm process.

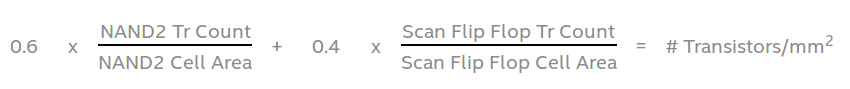

Mark goes on to say a metrics are needed, and manufacturers should disclose their logic transistor density in units of MTr/mm2 (millions of transistors per square millimeter), using the following formula combining NAND and Scan Flip Flop (SFF) cell areas.

He also explains SRAM cell size should be reported separately since there’s a wide variety of SRAM-to-logic ratios in different chips.

He also explains SRAM cell size should be reported separately since there’s a wide variety of SRAM-to-logic ratios in different chips.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress