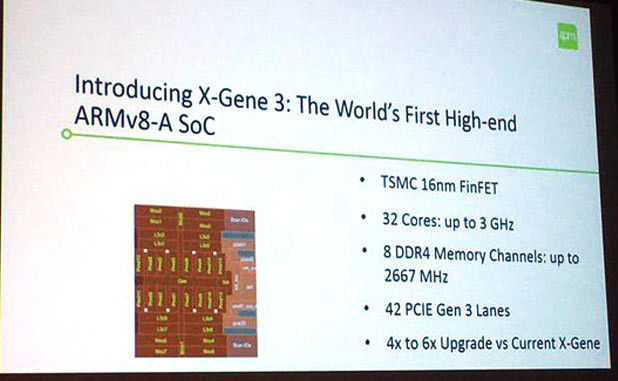

MACOM, having recently completed the acquisition of AppliedMicro, has now announced sampling of X-Gene 3 Server-on-a-Chip (SoC) with 16-nanometer FinFET process technology. X-Gene 3 features 32-core ARMv8 cores clocked at up to 3.0 GHz, 8 DDR4 channels, 42 PCIe Gen 3 lanes, SATA 3.0 and USB 3.0.

X-Gene 3 SoC key features and specifications

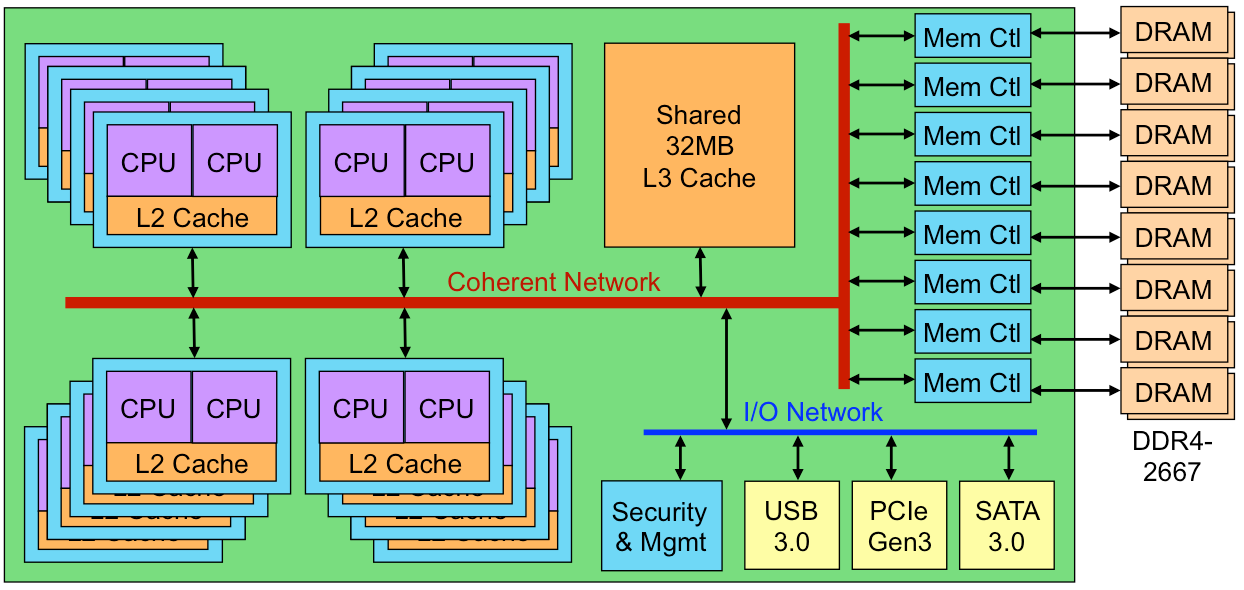

- CPU – 32x 64-bit ARMv8 cores @ up to 3.0 GHZ (base freq.) / 3.3 GHz (turbo freq.)

- Cache – 32MB L3 cache

- Memory IF – 8x DDR4-2667 channels with ECC and RAS supporting up to 16DIMMs for up to 1TB RAM

- Storage – SATA 3.0 interfaces

- 42x PCIe Gen 3 lanes with 8x controllers

- USB 3.0 interfaces

- Max. TDP – 125 Watts (Expected)

- Process – 16nm FinFET TSMC

X-Gene 3 is said to offer 4 to 6 better performance compared to X-Gene 2, and match “comparable x86 processors in CPU throughput, per-thread performance and power efficiency, while offering advantages in memory bandwidth and total cost of ownership”.

A white paper by the Linley group has some more insights about the performance:

The company expects the chip to deliver a SPECint_rate2006 (peak) score of at least 500 when running at its peak speed of 3.3GHz and DDR4-2667 and with some additional hardware and compiler tuning. This score is well ahead of that of any other ARM processor and similar to that of mainstream Xeon E5 processors.

In addition, the processor should achieve a single-thread SPEC_int2006 (peak) score of 24. Other CPU tests such as CoreMark and Dhrystone deliver similarly impressive results, outscoring leading ARM cores such as Cortex-A72 and custom designs from Cavium, Qualcomm, and Samsung. With eight DDR4 channels, X-Gene 3 also posts excellent scores on memory tests. For example, the processor scores 67.1GB/s on Stream Copy using DDR4-2133 and could exceed 80GB/s when it uses DDR4-2667.

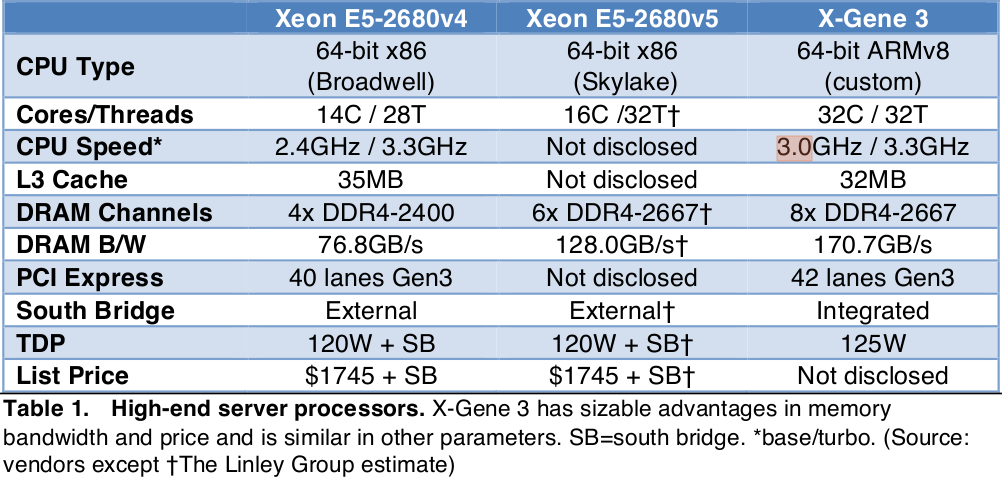

They also compared X-Gene 3 SoC directly to Xeon E5 processor in the table below using numbers provided by vendors, or estimates, not independent benchmarks.

MACOM’s new SoC appears to have the edge when it comes to memory bandwidth, however, they note that X-Gene 3 lags Xeon E5 in floating-point performance, X-Gene 3 will still do well on integer-only workloads such as deep learning used for voice services (e.g. Alexa), image classification, and other tasks.

MACOM is now shipping X-Gene 3 to selected partners. Some publicly available documents for APM883xxx-X3 (codename for X-Gene 3) should eventually be available on APM website.

Via Hexus, and thanks to Tadej for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress