lowRISC project aims to produce a completely open-source SoC (System-on-Chip) based on the 64-bit RISC-V instruction set architecture, as well as a corresponding development board, thus eventually producing a fully open hardware systems. The project has now announced its first release “tagged memory preview release” with a tutorial explaining how this has all been designed, and how to run simulations with software tools, or FPGA boards such as Zedboard.

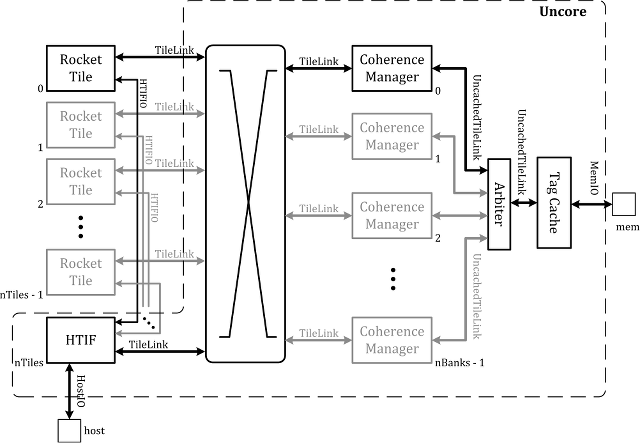

The project is based on Rocket core, written in Chisel language by the RISC-V team at UC Berkeley. Chisel can generate code to produce a cycle-accurate C++ emulator, Verilog optimised for FPGAs or Verilog for use in an ASIC flow.If you want to try it out, you’ll need a Linux machine, preferably running Ubuntu 14.04 64-bit, with GNU GCC 4.8 installed, and follow the tutorial in order to get the source code, and build tools such as riscv64-unknown-elf-gcc compiler, and Spike simulator, as well as a RISC-V Linux kernel. Finally, they’ll show you how to run various simulations using Spike, the C++ emulator, or an FPGA board.

This is only a first step, and much more work is needed, with the organization expecting to provide more features in the next releases including “tag support in the Spike simulator and support for the L2 cache, as well as a better ISA and core support for tags”, and later on, the development of an “untethered version of the SoC with the necessary peripherals”.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress