Before the BeagleBone and BeagleBone Black boards based on TI Sitara processor, there were BeagleBoard (-xM) boards powered by TI OMAP3 processors, and Beageboard.org and Texas Instruments are now working on their next open source hardware board with BeagleBoard-X15 powered by TI Sitara AM572 dual core Cortex A15 SoC.

Since Beagleboard-X15 has not been formally announced, there’s no picture, and we don’t have the full details yet, but here are the expect technical specifications:

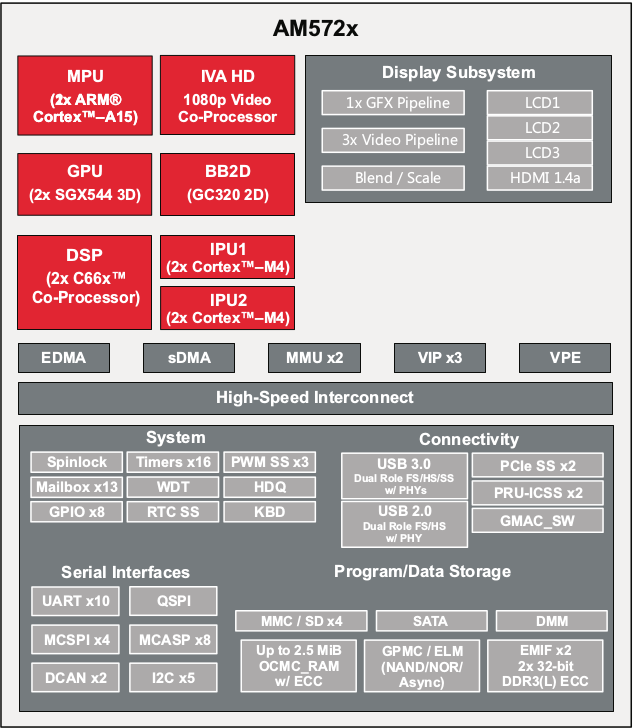

- SoC – Texas Instruments Sitara AM5728 dual core Cortex A15 processor @ 1.5 GHz, with PowerVR SGX544-MP2 3D GPU, Vivante GC320 2D GPU, 2x Cortex M4 cores, dual core C66x DSP, and IVA (Image and Video Accelerator) for 1080p video decode (H.264, VC-1, MPEG 1/2/4, AVS, etc..)

- System Memory – 2GB DDR3L with dual 32-bit buses

- Storage – 4GB eMMC, micro SD slot, and eSATA interface

- Video I/O – HDMI out up to 1080p60, LCD port, and Video IN

- Audio I/O – HDMI out, analog audio In/Out

- Connectivity – 2x Gigabit Ethernet ports

- USB – 3x USB 3.0 ports

More details will eventually show up on BeagleBoard-X15 Wiki (currently empty), in the meantime you can always check the boot log. Pricing and availability info are not available either, but the board will hopefully start selling in Q1 2015, or Q2 at the latest. is scheduled to launch in late February of 2015.

Texas Instruments has not formally announced their AM5x processor, but you can already get all details about AM5728 and AM5726 processors (codenamed J6/Vayu”), since the company has published a 7,229 pages “AM572x ARM Processor Technical Reference Manual“. There’s also a single core Cortex A15 processor family called AM571x “J6Eco” that should become available this quarter with AM5716 and AM5718.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress