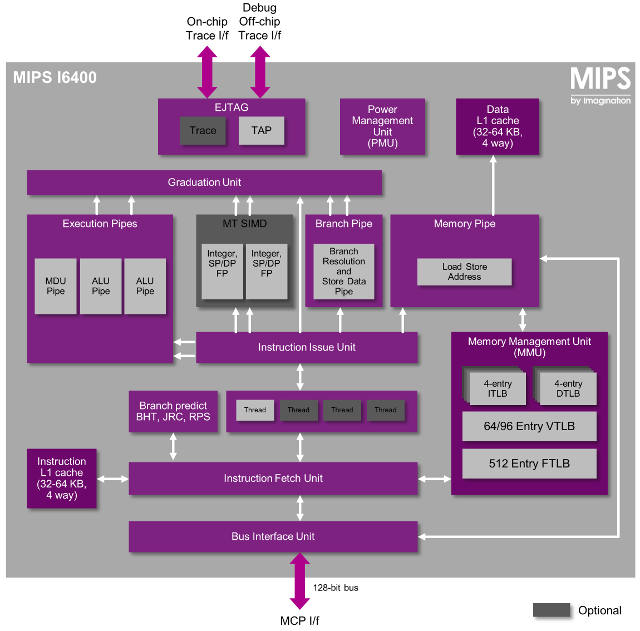

Imagination technologies has just announced their MIPS I6400 64-bit core for applications including embedded, mobile, digital consumer, advanced communications, networking and storage. MIPS I-class I6400 CPU family features a 64-bit architecture, hardware virtualization, multi-threading, multi-core and multi-cluster coherent processing, and MIPS32 code will run on MIPS64.

The key features of these MIPS64 cores are listed as follows:

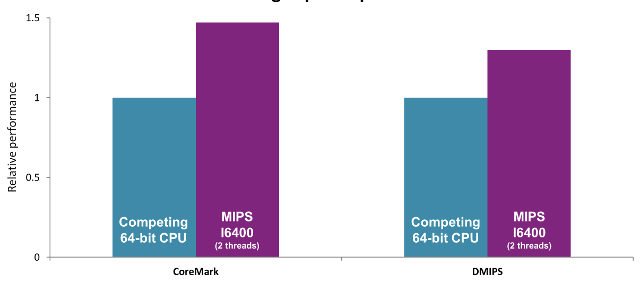

- Efficient, scalable 64-bit performance – The company claims MIPS I6400 achieves over 50% higher CoreMark performance and 30% higher DMIPS compared to “leading competitors in its class”.

- Hardware multi-threading – Supports up to four hardware threads per core, and simultaneous multi-threading (SMT) technology leads to higher utilization and CPU efficiency. Preliminary benchmarking shows that adding a second thread leads to performance increases of 40-50% on benchmarks such as SPECint and EEMBC’s CoreMark, with less than a 10% cluster area increase.

- Hardware virtualization – Includes support for up to 15 secure/non-secure guests.

- Next-generation security – The solution scales to support secure content delivery, secure payments, identity protection and more across multiple applications and content sources.

- Power management – With PowerGearing for MIPS, the I6400 has the ability to provide a dedicated clock and voltage level to each core in a heterogeneous cluster, while maintaining coherency across CPUs so that sleeping cores only need to wake when needed.

- FPU with single and double precision capabilities.

- 128-bit SIMD – The I6400 features 128-bit SIMD support, built on MIPS SIMD architecture which adheres to true RISC philosophy, with instructions defined to be easily supported within high-level languages such as C or OpenCL. The SIMD in the I6400 supports a wide variety of integer (8, 16, 32 and 64-bit) and floating point (32, 64-bit) data types suitable for various computationally-intensive use cases.

- Next-generation multicore coherency – Supports multicore configurations of up to six cores per cluster where multiple cores on a single cluster can have different synthesis targets, and operate at different clock frequencies and voltages. The Coherency Manager fabric implements hardware pre-fetching, wider buses and lower latencies compared to previous generations.

- Scalable, multi-cluster coherency – I6400 cores are designed to be delivered in diverse combinations of threads, cores and clusters, supporting multi-cluster fabric configurations up to 64 clusters.

The chart above shows better performance of MIPS I6400 with two threads compared to “competing 64-bit CPU”, which could either be ARM Cortex-53 / Cortex A57, or Intel Atom “Bay Trail” processors, so it’s difficult to get an idea of the actual performance compared to the competition. What’s clear is that multiple threads should improve performance in some benchmarks, and application such as web browsers.

MIPS Release 6 architecture also introduces new instructions that are said to accelerate performance for several workloads commonly found in Android, including JIT compilation, Javascript, web browsing, PIC (Position-Independent Code) for Android.

MIPS I6400 will be optimized for 32-bit and 64-bit operating systems including Android L which will support MIPS64. The company will provides software, tools and applications for the new cores, which will be supported by prpl open source foundation. MIPS64 r6 architecture is already supported in QEMU, and source code available on Prpl foundation’s github account.

MIPS I6400 license is already being used by “leading partners”, with general availability scheduled for December 2014, which probably means MIPS I6400 based SoCs should become available sometimes in H2 2015, or early 2016. You can also read Imagination’s blog post for a few more details.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress