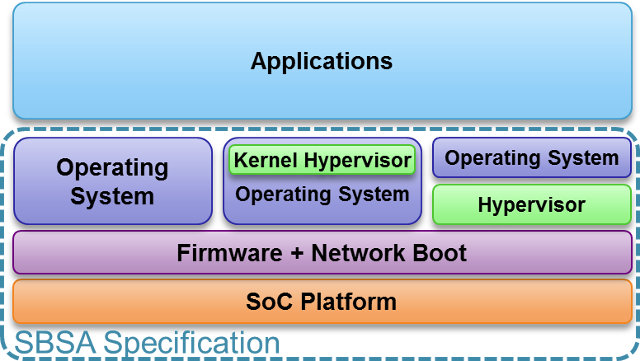

64-bit ARM based servers should hit the market later this year or earlier in 2015 with SoCs such as Applied Micro X-Gene or AMD Opteron A1100. ARM still has the lead in terms of efficiency with a lower dollar per watt ratio, but Intel is closing in with their new Avoton server-on-chips. However, there’s one aspect where Intel is clearly in the lead: standardization and compatibility. ARM is very flexible, and allow SoC designers to create more or less what they want, but it comes at the cost that most ARM based systems are not capable of running mainline Linux, and instead use vendor trees. With many applications, that may not be critical, but when it comes to data-centers, companies want to be able to run the latest Linux version with the latest security patches as soon as possible, and want to lower the total cost of ownership (TCO), so they don’t want to spend considerable resources to handle different hardware platform. This is currently not feasible, but ARM together with their partners, including silicon vendors such as AMD, Applied Micro Cavium, and Texas Instruments, and software companies such as Canonical, Citrix, Linaro, Microsoft, Red Hat and SUSE, have jointly announced the System Base Architecture Specifications to standardize all ARM based servers so that one single OS image can run on all ARMv8-A server.

The SBSA specification does not address the application layer, but it standardizes low-level CPU and SoC attributes such as timers, interrupt controllers, watch dog timers, performance counters and also specifies minimum hardware requirements that firmware and OS vendors expect to be present. To be compliant, server will also need to run industry standards for bootloader and firmware, with all hardware being describable or discoverable. There are three levels of standardization:

- Level 0 – Defines CPU Architecture, Interrupt Controller, Memory Map, IO Visualization, Clock and Timer Subsystem, Wake up semantics, Power State Semantics and Peripheral Subsystems

- Level 1 – Based on Level 0 with extra requirements with regards to CPU Architecture, Interrupt Controller, Clock and Timer Subsystem, Watchdogs, Requirements on power state semantics, and Peripheral Subsystems

- Level 2 – Based on Level 1 with extra requirements with regards to CPU Architecture, Interrupt Controller (inc. PPI assignments), Memory Map, Requirements on power state semantics, IO Visualization, Clock and Timer Subsystem, Wake up semantics and Watchdogs

Most recent ARM SoCs, such as Opteron A1100, are likely to only support Level 0 or 1 at first. I haven’t read the specifications in details, but for example, Level 0 defines SoC with up to 8 CPU cores, Level 1 is still limited to a maximum of 8 cores, but adds minimum requirements for the number of PMU counters, watchpoints and breakpoints, and Level 2 supports SoC with up to 2^28 (268,435,456) CPU cores which is the maximum supported by GICv3 architecture.

If you want to find out the details, you can download the specifications from ARM website, after registration and accepting an EULA. Alternatively, since the document is non-confidential, the EULA is also listed in page 2 to 4 of the document, you can download it directly here.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress