Thanks to Omegamoon (and this brother) we already have instructions to connect the UART pins on MK808 in order to access the serial console. He’s done it again with MK908 mini PC featuring Rockchip RK3188.

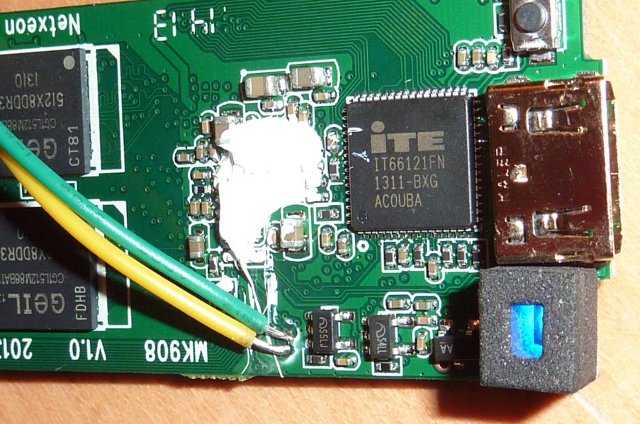

Tx and Rx pads are located on the RAM chips side, and he has connected the green wire to Tx (Going to Rx on TTL debug board), and a yellow wire to Rx (Tx on debug TTL board).

A ground pad is available on the other side of the board.

Since I got a sample for review from Geekbuying, I decided to give a try myself. The pad are quite small, so this may require patience, but it’s perfectly feasible. I wanted to keep the device closed, so I passed the wires through the ventilation holes (enlarging them a bit with a precision screwdriver), put back the main heatsink on RK3188, and reassembled the enclosure. I did not include the thin heatsink on the other side of the board. Finally, I inserted a 3-pin right angle header in the casing, solder the wires, and connected a USB to TTL debug board.

Final check is to check the connection is fine with minicom configured on /dev/ttyUSB0 with 115200 8N1:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 |

BUILD=====4 GetRemapTbl flag = 0 OK! 53209 unsigned! SecureBootEn = 0 Boot ver: 2013-02-01#1.02 start_linux=====64906 1609103 Starting kernel...@0x60408000 [ 0.000000] Initializing cgroup subsys cpu [ 0.000000] Linux version 3.0.36+ (ouyang_V_101j1) (gcc version 4.4.3 (GCC) 3 [ 0.000000] CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=10c5387d [ 0.000000] CPU: VIPT nonaliasing data cache, VIPT aliasing instruction cache [ 0.000000] Machine: RK30board [ 0.000000] memory reserve: Memory(base:0x91800000 size:80M) reserved for <i> [ 0.000000] memory reserve: Memory(base:0x90d00000 size:11M) reserved for [ 0.000000] memory reserve: Memory(base:0x90700000 size:6M) reserved for [ 0.000000] memory reserve: Total reserved 97M [ 0.000000] Memory policy: ECC disabled, Data cache writeback [ 0.000000] bootconsole [earlycon0] enabled [ 0.000000] CPU SRAM: copied sram code from c0c17000 to fef00100 - fef01f10 [ 0.000000] CPU SRAM: copied sram data from c0c18e10 to fef01f10 - fef02640 [ 0.000000] sram_log: $1 f - . jZiYhX @ [ 0.000000] L310 cache controller enabled [ 0.000000] l2x0: 16 ways, CACHE_ID 0x4100c0c8, AUX_CTRL 0x76050001, Cache sB [ 0.000000] DDR DEBUG: version 1.00 20130130 [ 0.000000] DDR DEBUG: DDR3 Device [ 0.000000] DDR DEBUG: Bus Width=32 Col=10 Bank=8 Row=16 CS=1 Total CapabiliB [ 0.000000] DDR DEBUG: init success!!! freq=396MHz [ 0.000000] DDR DEBUG: DTONE=0x1, DTERR=0x0, DTIERR=0x0, DTPASS=0x4, DGSL=1 0 [ 0.000000] DDR DEBUG: DTONE=0x1, DTERR=0x0, DTIERR=0x0, DTPASS=0x4, DGSL=1 0 [ 0.000000] DDR DEBUG: DTONE=0x1, DTERR=0x0, DTIERR=0x0, DTPASS=0x4, DGSL=1 0 [ 0.000000] DDR DEBUG: DTONE=0x1, DTERR=0x0, DTIERR=0x0, DTPASS=0x4, DGSL=1 0 [ 0.000000] DDR DEBUG: ZERR=0, ZDONE=0, ZPD=0x0, ZPU=0x0, OPD=0x0, OPU=0x0 [ 0.000000] DDR DEBUG: DRV Pull-Up=0xb, DRV Pull-Dwn=0xb [ 0.000000] DDR DEBUG: ODT Pull-Up=0x2, ODT Pull-Dwn=0x2 .... </i> |

Good! I can also type in the console, so both Tx and Rx are working fine. I love when everything goes according to plans!

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress